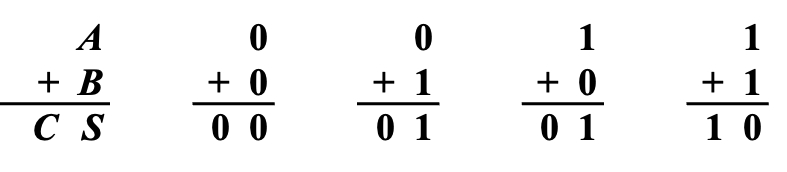

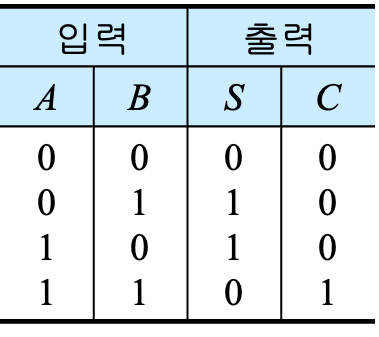

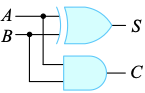

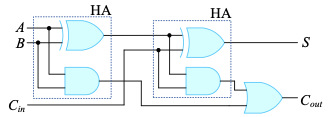

1. 반가산기(Half-adder, HA)

- 한 자리 2진수 2개를 입력하여 합(sum: S)과 캐리(carry: C, 자리올림)를 계산하는 덧셉 회로

- C는 A와 B가 모두 1인 경우에만 1이 되고, S는 A와 B가 둘 중 하나만 1일 때 1이 됨

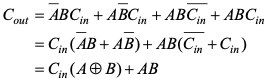

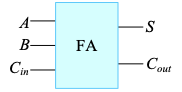

2. 전가산기(full-adder, FA)

- 자리 올림수를 고려하여 만든 덧셈 회로

- 두 개의 2진수 입력 A, B와 아랫자리로부터 올라온 캐리 Cin을 포함하여 한 자리 2진수 3개를 더하는 조합논리회로

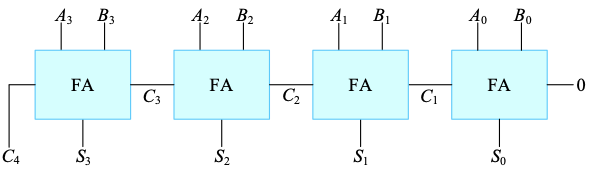

3. 병렬가감산기(parallel-adder/substracter)

- 병렬가산기: 전가산기 여러 개를 병렬로 연결한 회로

- 병렬가감산기: 병렬 가산기의 B입력을 부호 S(sign)와 XOR하여 전가산기의 입력으로 사용함으로써 덧셉과 뺄셈이 모두 가능한 회로

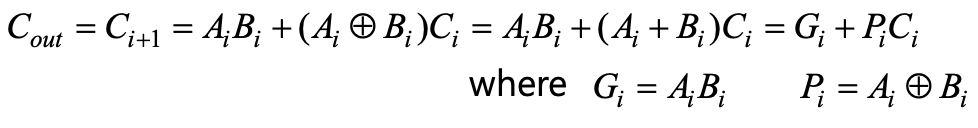

4. 고속 가산기(high-speed-adder)

- 병렬가산기의 단점(아랫단에서 윗단으로 전달되는 자리올림수 때문에 속도가 매우 느림)을 해결하기 위해 캐리 예측 가산기(carry-look-ahead-adder, CLA)를 사용함

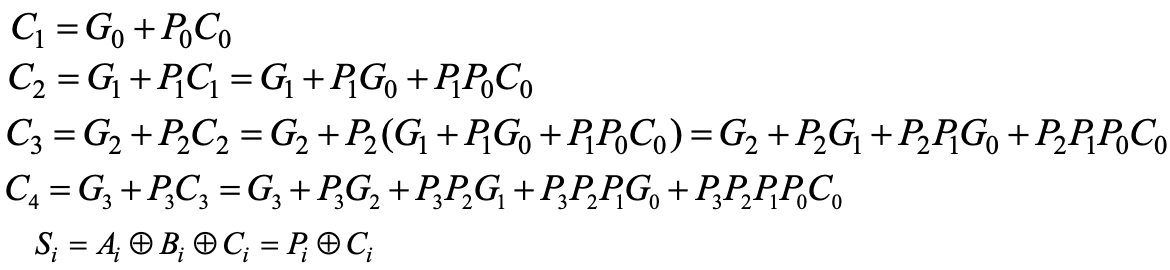

- CLA의 원리

캐리를 미리 계산하여 위로 보냄

Ai, Bi 모두가 1일 때, 또는 Ai, Bi 둘 중에 하나가 1이고 Ci 가 1일 때 캐리가 발생하므로

4비트 가산기에서 위 식을 써보면

- 캐리예측가산기는 Si, Pi, Gi 를 발생시키는 부분전가산기(PEA)와 위의 식 C1, C2, C3, C4 을 발생하는 캐리예측 회로로 구성됨

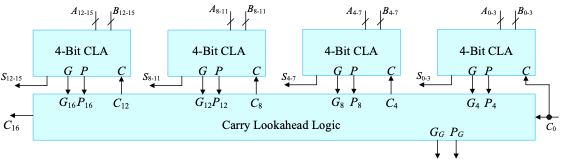

- 4비트 캐리예측가산기를 하나의 모듈로 만들어서 16비트 캐리예측가산기를 만들어 사용함

5. BCD 가산기

- BCD 코드는 2진수와 달리 표현범위가 0에서 9까지 이므로, BCD 계산을 하려면 결과를 보정해야함

- 2진수 합의 결과가 1010~1111인 경우 보정(+6)

'Lecture > Logic circuit' 카테고리의 다른 글

| [Chapter1 조합논리회로] 02. 비교기 (0) | 2021.04.26 |

|---|